Sie is all the cont The Core Memory Project Technical Depreses Manual www.thecorememory.com

Preface

This manual describes the NCR 286 Card (to be referred to as processor board) and its interfaces. Both the power-fail recovery (PFR) card and the non-power fail recovery (NPFR) card descriptions are included in this publication. The Card supports three processing speeds, 6.0MHz, 8.0MHz, and 10.0MHz, and allows operation at two speeds. The speed is user selectable and may be set to either 6.0MHz and 8.0MHz or 6.0MHz and 10.0MHz depending on the processor board. The default speed is 6.0MHz for both boards. The higher speed is determined by the frequency of the crystal oscillator. The 6/8 board has a 16.0MHz crystal and the 6/10 board has a 20.0MHz crystal. These boards utilize NCR's split board architecture (SBA), in which major system components are placed on different pluggable cards.

The information in this publication is for reference and is intended for system integrators and anyone else who needs to understand the design of the NCR 286 Cards.

This manual consists of eight chapters:

- The first chapter gives general information about the board including its physical dimensions, electrical, environmental, and safety characteristics, and shipping considerations.

- The second chapter gives the functional description of the board's main components and describes its interfaces, system timing, address maps, and connectors.

- Chapter three contains information on switch settings, jumper strappings, and adjustments.

- O Chapter four describes level 0 diagnostics.

• Chapter five contains pin-outs for the main imponents on the The Core Merhory Project

- Chapter six contains board specifications information.

- Chapter seven contains logic diagrams.

- Chapter eight contains the 80286 instruction set.

Contents

# 286 Card Technical Reference

| Chapter 1 General Information INTRODUCTION                                                                                                                                                                          | [-]                         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| PHYSICAL DESCRIPTION 1 Electrical Characteristics 1 Current Requirements 1 Environmental Characteristics 1 Safety Characteristics 1 FCC Notice 1 Socket-Mounted Components 1 Shipping Considerations 1 References 1 | 1-2<br>-6<br>-6<br>-7<br>-7 |

| Chapter 2 Functional Description PROCESSOR BOARD                                                                                                                                                                    |                             |

| 80286 Microprocessor                                                                                                                                                                                                | -1                          |

| Random Access Memory (RAM)                                                                                                                                                                                          | -3                          |

| RAM Memory Reset Timing (PFR)                                                                                                                                                                                       | -4                          |

| Reset Generation (PFR)                                                                                                                                                                                              | -4                          |

| Read Only Memory (ROM)2-                                                                                                                                                                                            | -6                          |

| Direct Memory Access (DMA)2-                                                                                                                                                                                        | 9                           |

| Fimer/Counter2-1                                                                                                                                                                                                    | 1                           |

| nterrupt Control2-1                                                                                                                                                                                                 | 1                           |

| Numeric Processor Extension                                                                                                                                                                                         | 2                           |

| CPU VLSI                                                                                                                                                                                                            | 3                           |

| ORAM Controller VLSI —                                                                                                                                                                                              |                             |

| Power Fail Recovery Board (PFR)2-1                                                                                                                                                                                  | 4                           |

| ORAM Controller VLSI —                                                                                                                                                                                              |                             |

| Non-Power Fail Recovery Board (NPFR)2-1                                                                                                                                                                             | 6                           |

|                                                                                                                                                                                                                     |                             |

| The | Core Memory Project                         |

|-----|---------------------------------------------|

|     | Core Memory Project Real-Time Clock VLSI    |

|     | Input and Output Control Line Functions2-19 |

|     | Multiplexed Bidirectional Address/Data Bus  |

|     | ALE - Multiplexed Address Strobe2-19        |

|     | IRQ - Interrupt Request                     |

|     | RESET                                       |

|     | PS - Power Sense                            |

|     | Address Map2-20                             |

|     | Periodic Interrupt Selection                |

|     | Alarm Interrupt Selection                   |

|     | Static CMOS RAM2-23                         |

|     | Update Cycle                                |

|     | RTC Registers2-25                           |

|     | Register A2-25                              |

|     | Update In Progress Bit2-26                  |

|     | Rate Selection Bits2-26                     |

|     | Register B2-26                              |

|     | SET                                         |

|     | Periodic Interrupt Enable Bit2-27           |

|     | Alarm Interrupt Enable Bit2-27              |

|     | Undate-ended Interrupt Enable Bit2-27       |

|     |                                             |

|     | Data Mode Bit2-27                           |

|     | 24/12 Bit                                   |

|     | Daylight Savings Enable Bit2-28             |

|     | Register C2-28                              |

|     | Interrupt Request Flag2-28                  |

|     | Periodic Interrupt Flag2-28                 |

|     | Alarm Interrupt Flag2-28                    |

|     | Update-Ended Interrupt Flag2-29             |

|     | B3 to B0                                    |

|     | Register D                                  |

|     | Valid RAM and Time Bit2-29                  |

|     | b6 to b0                                    |

|     | Keyboard Interface2-30                      |

|     | 8742 Controller2-31                         |

|     | Software Speed Switching2-32                |

|     | Address Maps2-32                            |

|     | Memory Address Map2-32                      |

|     | I/O Address Map2-34                         |

| CONNECTO        | )KS              | * * * * * * * * * * * * |           | 2-1       |

|-----------------|------------------|-------------------------|-----------|-----------|

| Battery Con-    | nector           |                         |           | 2-3       |

| Kaubaawl La     | ector            |                         |           |           |

| Keyboard 130    | ck/LED Speed     | indicator Con           | nector    | 2-1       |

| Reyboard/Po     | wer Good Conne   | ector                   |           | 2-(       |

| Expansion it    | AM Connector.    |                         |           | 2-3       |

| Laria Ci        | tors             |                         |           | 2-5       |

| Detroyal Co     | ls and Their Fu  | nctions                 |           | 2,4       |

| Pata anti Co    | ontrol Signals   | •••••                   |           | 2-4       |

| DOM: DIOC       | ng               |                         |           | 2-0       |

| ROW BIOS.       |                  |                         |           | 2-5       |

| Setup           |                  |                         |           | 2-5       |

| Chapter 3       | Switches,        | Jumpers, a              | and Adius | stments   |

| SWITCH SE       | TTINGS           | rutus, assaulis ist     |           | 9.        |

|                 |                  |                         |           |           |

| JUMPER ST       | RAPPING          |                         |           | 9.        |

| High Perform    | nance Option     |                         |           | ۹.        |

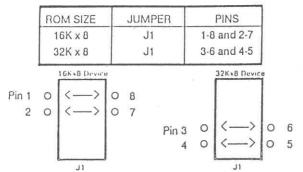

| ROM/EPRON       | A Size Select    |                         |           | 9.        |

| Description O   | f Jumpers (NPI   | (R)                     |           | 9.        |

| Speed Selection | on Switch        |                         |           | 9         |

| Power Fail Pr   | otection Mode (  | PFR)                    |           | 2         |

| Non-Power Fr    | all Protection M | ode (PFR)               |           | 9.        |

| Memory Confi    | iguration (PFR)  |                         |           | 3.        |

| Wait State Set  | ttings (PFR)     |                         | 110000000 | 3.        |

| Extended Refi   | resh (PFR)       |                         |           | 0.1       |

| Description ()  | f Jumpers (PFR   | )                       |           | 3-(       |

|                 | NTS              |                         |           |           |

| MIND OUT MEN    | (10              |                         |           | 3-7       |

| Chapter 4       | Diagnostics      | 3                       |           |           |

| LEVEL 0 DIA     | GNOSTICS         |                         |           | (1)       |

| Level 0 Diagno  | stics Messages . |                         |           | 4.9       |

| Speaker Beep    | s                |                         |           | 4.9       |

| Video Display   | Messages         |                         |           | 1.9       |

| Level U Diagno  | Stics Phases     |                         |           | 4.0       |

| Initial Process | sor Board Tests  |                         |           | 4.14.2    |

| rest and Initi  | alli2e* .        |                         |           | 4.4       |

| System Confis   | guration Verific | ation                   |           | 4.0       |

|                 |                  |                         |           | 0.6 ceres |

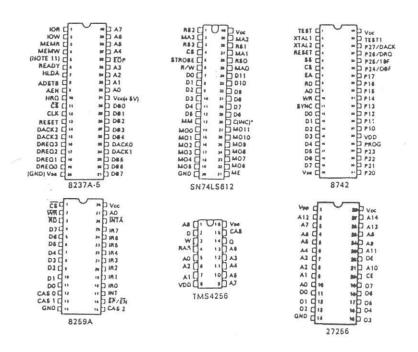

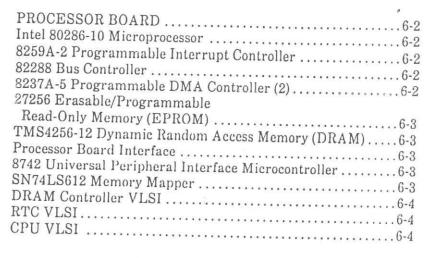

# The Core Memory Project Setting The System Configuration ......4-9 Integrated Circuit Component Chapter 5 Pin-Out Configurations Integrated Circuit Component Pin-Out Configurations ......5-1 Chapter 6 Specifications PROCESSOR BOARD ......6-2 8259A-2 Programmable Interrupt Controller ..............6-2 8237 A-5 Programmable DMA Controller (2)...................6-2 27256 Erasable/Programmable Read-Only Memory (EPROM) ......6-3 TMS4256-12 Dynamic Random Access Memory (DRAM) .....6-3 SN74LS612 Memory Mapper ......6-3 Chapter 7 Logic Diagrams Chapter 8 80286 Instruction Set

#### LIST OF FIGURES

| Figure 1-1  | Power fail recovery                        |

|-------------|--------------------------------------------|

|             | processor board layout (PFR)1-             |

| Figure 1-2  | Non-power fail                             |

|             | recovery board layout (NPFR)1-4            |

| Figure 1-3  | Power connector pin-outs1-5                |

| Figure 1-4  | Current requirements                       |

| Figure 1-5  | Environmental characteristics 1-6          |

| Figure 2-1  | System performance2-2                      |

| Figure 2-2  | Reset timing diagram (PFR)2-4              |

| Figure 2-3  | ROM address map2-6                         |

| Figure 2-4  | Power fail recovery board                  |

|             | functional block diagram (PFR)2-7          |

| Figure 2-5  | Non-power fail recovery board              |

|             | functional block diagram (NPFR)2-8         |

| Figure 2-6  | Page register addresses2-10                |

| Figure 2-7  | DMA controller command code addresses2-10  |

| Figure 2-8  | Timer counters2-11                         |

| Figure 2-9  | Hardware interrupt assignments2-11         |

| Figure 2-10 | System speed/coprocessor                   |

|             | type requirements2-12                      |

| Figure 2-11 | CPU VLSI block diagram2-13                 |

| Figure 2-12 | DRAM controller VLSI (PFR)2-14             |

| Figure 2-13 | DRAM controller VSLI (NPFR)2-16            |

| Figure 2-14 | RTC VLSI block diagram2-17                 |

| igure 2-15  | RTC RAM I/O address map2-18                |

| Figure 2-16 | RAM and control registers address map2-21  |

| Figure 2-17 | Time, calendar, and alarm data modes2-21   |

| Figure 2-18 | Register A rate selection bit settings2-22 |

| eigure 2-19 | Update-ended and                           |

|             | periodic interrupt relationships2-25       |

| igure 2-20  | Register A bit functions2-26               |

| igure 2-21  | Register B bit functions2-26               |

| igure 2-22  | Register C bit functions2-28               |

| igure 2-23  | Register D bit functions2-29               |

| 'igure 2-24 | Keyboard connector pin-out2-30             |

| igure 2-25  | UPI port description2-31                   |

| igure 2-26  | UPI test pin definitions 2-31              |

# General Information

| INTRODUCTION               | 1-  |

|----------------------------|-----|

| PHYSICAL DESCRIPTION       | 1-2 |

| Electrical Characteristics | 1_5 |

| Current Requirements       | 1 0 |

| Safety Characteristics     | 1 7 |

| FCC Notice                 | 1-7 |

| Shipping Considerations    | 1.7 |

| References                 | 1-8 |

| he | Core Memory F             | Project<br>Speed/performance comparison                                           |

|----|---------------------------|-----------------------------------------------------------------------------------|

|    | Figure 2-28               | Memory address map                                                                |

|    | Figure 2-29               | Dedicated I/O addresses2-34                                                       |

|    | Figure 2-30               | Reserved I/O addresses                                                            |

|    | Figure 2-31               | Speaker connector pin-out2-36                                                     |

|    | Figure 2-32               | Battery connector pin-out2-36                                                     |

|    | Figure 2-33               | Keyboard lock/LED speed                                                           |

|    |                           | indicator connector pin-out2-37                                                   |

|    | Figure 2-34               | Keyboard/power good connector pin-out2-37                                         |

|    | Figure 2-35               | Expansion RAM connector pin-out2-38                                               |

|    | Figure 2-36               | 62 Pin card edge                                                                  |

|    |                           | connector, 8-bit bus interface2-39                                                |

|    | Figure 2-37               | 36-Pin card edge                                                                  |

|    |                           | connector, 16-bit bus interface2-40                                               |

|    | Figure 2-38               | Input logic level voltages2-45                                                    |

|    | Figure 2-39               | Input loading characteristics2-45                                                 |

|    | Figure 2-40               | Output logic level voltages2-45                                                   |

|    | Figure 2-41               | Signals BA1-19, OSC, and BBHE loading2-46                                         |

|    | Figure 2-42               | Signals +BRESET, +AEN, BSELALE,                                                   |

|    |                           | BD0-15, -IOW, -IOR, -MEMW,                                                        |

|    | <b>D</b> .                | AND EXPA17-23 loading characteristics2-46                                         |

|    | Figure 2-43               | Signals +BSYSCLK, -REFRESH,                                                       |

|    |                           | -CMEMR, -CMEMW, MEMR,                                                             |

|    |                           | AND BA0 loading characteristics 2-46                                              |

|    | Figure 2-44               | Signal T/C loading characteristics2-47                                            |

|    | Figure 2-45               | Signal -REFRESH                                                                   |

|    | 12: 0 40                  | loading characteristics2-47                                                       |

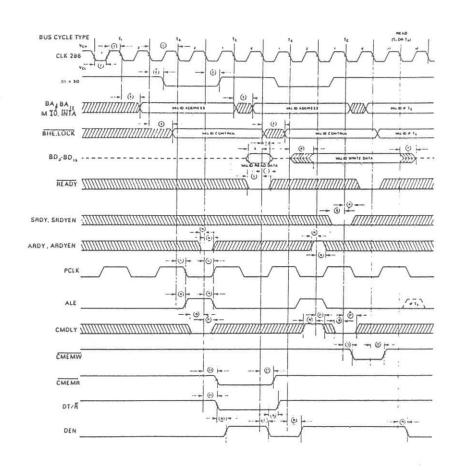

|    | Figure 2-46               | System bus timings                                                                |

|    | Figure 2-47<br>Figure 3-1 | System timing diagram2-49                                                         |

|    | Figure 3-1<br>Figure 3-2  | Video display switch settings3-1                                                  |

|    | Figure 3-2                | ROM/EPROM size select strapping3-2                                                |

|    | Figure 3-4                | Processor board jumper strapping (NPFR)3-2<br>Initial power-up speed strapping3-3 |

|    | Figure 3-4                | Power fail protection strapping (PFR)                                             |

|    | Figure 3-6                | Non-power fail protection strapping (PFR)3-4                                      |

|    | Figure 3-7                | Memory configuration strapping (PFR)3-4                                           |

|    | Figure 3-8                | Wait state strapping (PFR)3-5                                                     |

|    | Figure 3-9                | Processor board jumper strapping (PFR) 3-6                                        |

|    | Figure 4-1                | SETUP menu4-10                                                                    |

|    | Figure 4-2                | Diagnostic LED test board                                                         |

|    | 00 1 1                    | Triaginostic That's test board                                                    |

# General Information

# INTRODUCTION

The processor board is an IBM-PC/AT-compatible single-board computer card that uses split board architecture (SBA). The board, designed for modularity and flexibility, is functionally PC/AT compatible in terms of processor speed, input/output port assignments, memory configuration, and expansion-bus interface.

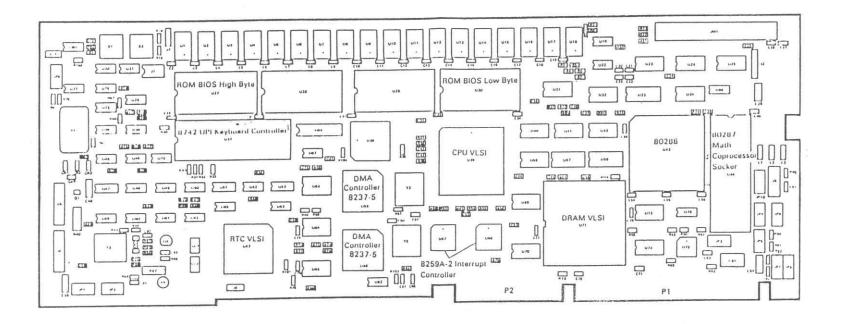

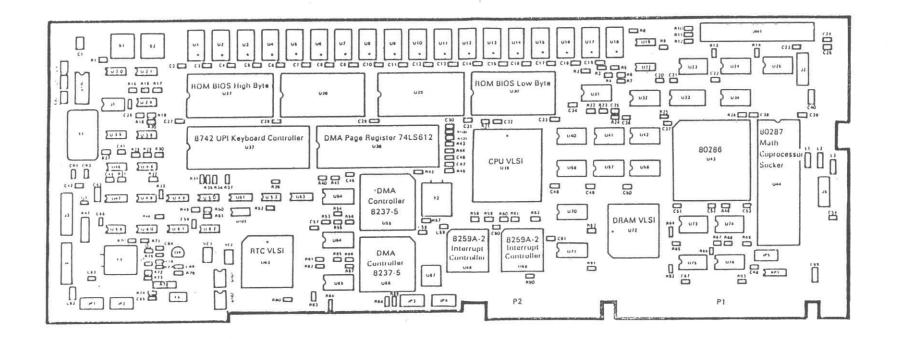

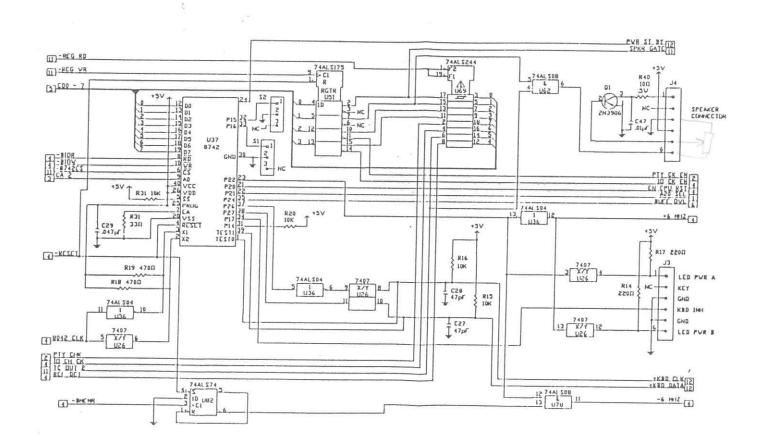

The board is designed on the PC/AT peripheral card form factor using state-of-the-art application-specific integrated circuits (ASIC), very large-scale integration (VLSI) technology, and surface-mount technology (SMT). Figures 1-1 and 1-2 show the location of the components on the board. Features of the processor board are:

- o Intel 80286 Microprocessor

- o DMA 7 channels

- o Three programmable timers

- e ROM memory 128KB

- a 24-bit address bus

- o 1GB virtual memory

- Keyboard port

- Software speed switching

- User selectable wait state

- o LED speed indicator

- Battery backup

- Base memory expansion to 640KB

PC/AT-standard peripheral

- o Multiple VLSI chips

- Pipelined bus interface

- Real-Time Clock (RTC)

- 16-level interrupt

- RAM memory 512KB

- 16-bit data bus

- 16MB real memory

- PC/AT compatible ROM BIOS

- 80287 coprocessor socket

- System clock

- · Keyboard entry lockout

- Speaker volume control

- card size

#### PHYSICAL DESCRIPTION

The processor board is a 4.8-inch by 13.15-inch, multilayered printed circuit board. It is an industry-standard PC/AT card-sized board.

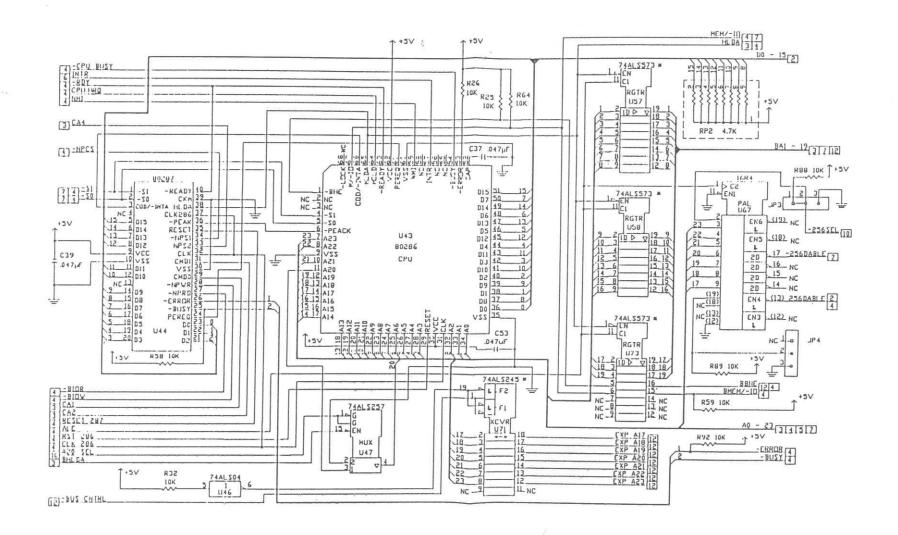

The key operating component is the INTEL 80286-10 16-bit microprocessor (U43) located on the right side of the board. Other major components on the card include:

#### Right side of board:

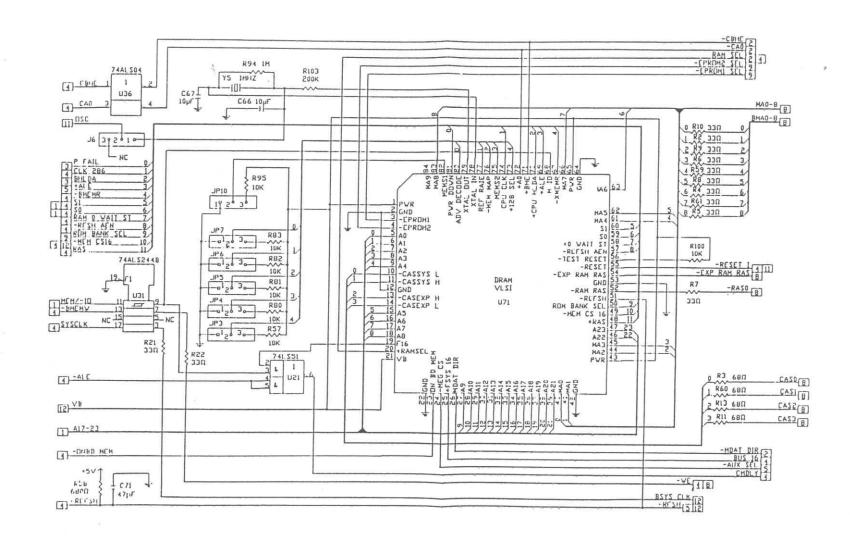

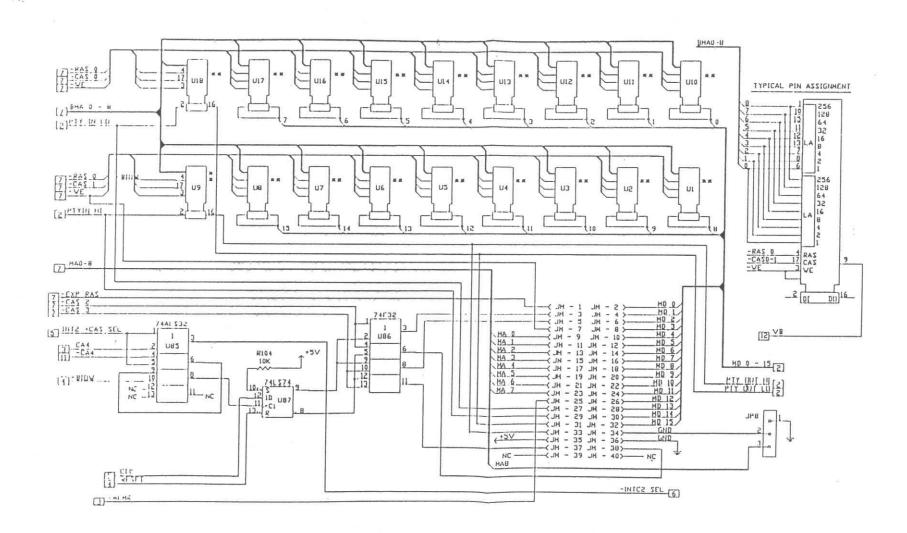

- o DRAM VLSI (NPFR board U72, PFR board U71)

- o 80287 math coprocessor socket (U44)

#### Center of board:

- CPU VLSI (U39)

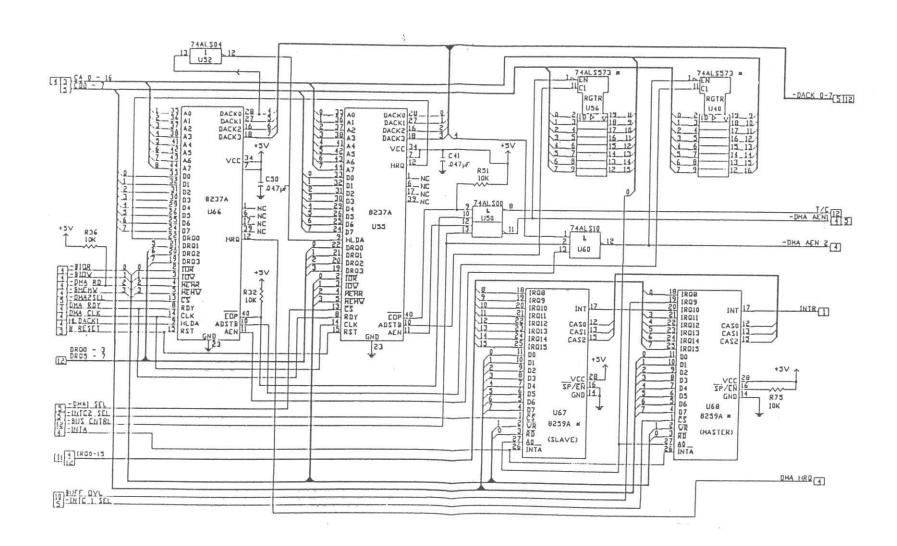

- 8259A-2 Interrupt Controllers (2) NPFR U68,U69/PFR U67,U68

- 8237-5 DMA controllers (2) U55,U66

- DMA page register 74LS612 (U38)

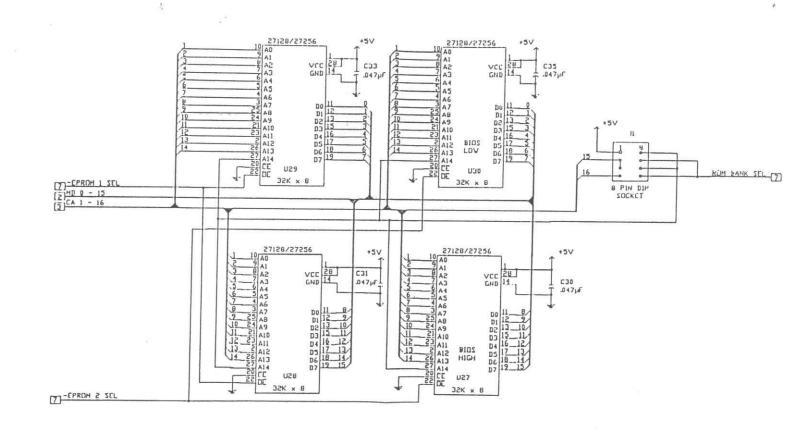

- ROM BIOS low byte (U30)

#### Left side of board:

- Real-Time Clock (RTC) VISI (U63)

- 8742 Universal Peripheral Interface (U37)

- ROM BlOS high byte (U27)

DC power is supplied to the board through the bus connector located on the bottom right of the board near the DRAM VLSI chip.

Mounted near the RTC VLSI chip are two adjustable capacitors: VC1 to trim the 14.318MHz clock and VC2 to trim the 32.768KHz crystal for the Time of Day clock.

Figure 1-1 Power fail recovery processor board layout (PFR)

X

Figure 1-2 Non-power fail recovery board layout (NPFR)

Also on the board are connectors for the following:

- o 6-pin 8-ohm speaker (J4)

- 5-pin battery back-up (PFR), 4-pin (NPFR) RTC/CMOS configuration table (J2)

- o 6-pin keyboard lock/LED speed indicator (J3)

- 10-pin keyboard/power good (J5)

- o 36-pin expansion RAM (JM1)

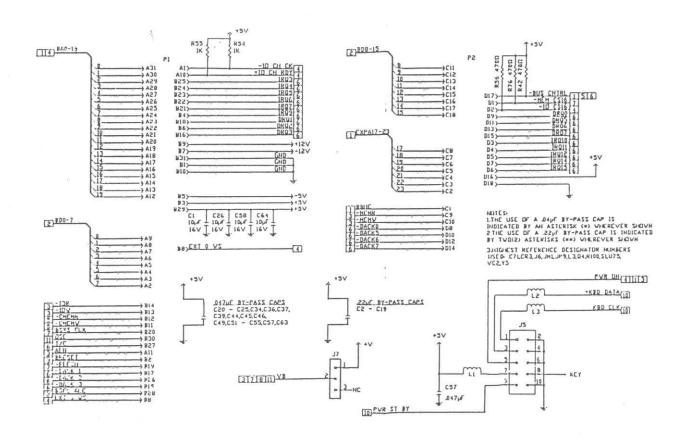

Below the Interrupt controller chip area are two board-edge bus connectors:

- e 62-pin 8-bit I/O bus signal interface (P1)

- o 36-pin 16-bit I/O bus signal interface (P2)

Also on the board are two banks of dynamic RAM. Each bank consists of nine chips; eight chips are for data and the ninth is for parity. These chips provide 512KB of base memory. RAM memory may be increased 128KB for a maximum of 640KB base memory.

# **ELECTRICAL CHARACTERISTICS**

DC power is provided to the board through the bus connector. Figure 1-3 shows the power input connector pin-outs.

| Pin | Voltage  |

|-----|----------|

| В3  | +5 volts |

| B29 | +5 volts |

| D16 | +5 volts |

| B1  | Ground   |

| B10 | Ground   |

| B31 | Ground   |

| D18 | Ground   |

Figure 1-3 Power connector pin-outs

#### **CURRENT REQUIREMENTS**

The current requirements are shown in Figure 1-4. Maximum current indicates a fully populated system board, including an 80287 math coprocessor and two extra EPROMs.

| Voltage | Voltage<br>Tolerance | Typical<br>Current | Maximum<br>Current |

|---------|----------------------|--------------------|--------------------|

| +12v*   | +-10%                | 0.0 mA             | 0.0 mA             |

| + 5v    | +- 5%                | 2.25 A             | 3.0 A              |

| - 5v*   |                      | 0.0 mA             | 0.0 mA             |

| -12v*   | +-10°%               | 0.0                | 0.0 mA             |

<sup>\* -5,+12</sup> and -12 volts are not used by this board.

Figure 1-4 Current requirements

#### **ENVIRONMENTAL CHARACTERISTICS**

The processor board withstands various environmental conditions during normal operation, shipment, storage, and handling as specified in Figure 1-5.

| RANGE                | DRY BULB<br>TEMPERATURE                  | RELATIVE<br>HUMIDITY                 | BAROMETRIC PRESSURE                     |

|----------------------|------------------------------------------|--------------------------------------|-----------------------------------------|

| Operating            | 10 C to 55 C<br>10 C Change<br>per hour  | 20% to 80%<br>10% Change<br>per hour | 105 to 69,000<br>Pascals up to 9850 ft. |

| Extreme<br>Power On* | 0 C to 60 C<br>10 C Change<br>per hour   | 10% to 95%<br>w/o<br>condensation    | Same for all ranges.                    |

| Storage              | -10 C to 50 C<br>15 C Change<br>per hour | 10% to 90%<br>w/o<br>condensation    |                                         |

| Transit              | -40 C to 60 C<br>20 C Change<br>per hour | 5% to 95%<br>w/o<br>condensation     |                                         |

<sup>\*</sup> NOTE: The extreme power-on range indicates limits which are likely if the heating or air conditioning plant fails or has not yet brought the room to operating conditions.

Figure 1-5 Environmental characteristics

#### SAFETY CHARACTERISTICS

The board is constructed of UL recognized material and processed by a UL recognized etching house. The board meets 94V2 flammability rating and is marked in accordance with UL procedures.

#### FCC NOTICE

The processor board, when operating in the final product configuration, is subject to FCC part 15J (USA) and/or FTZ (Germany) measurements of conducted and radiated radio frequency emissions, depending on the product classification. The board, as delivered, is neither Class A VERIFIED nor Class B CERTIFIED. The final product must be tested to establish its compliance with the applicable emissions regulations.

# SOCKET-MOUNTED COMPONENTS

The processor board contains the following socket-mounted components:

- ROM BIOS chips (U27,U30)

- Keyboard Controller (U37)

- 80286 Microprocessor (U43)

- o DRAM Controller VLSI (U71)

The pin assignments for these components are shown in the "Integrated Circuit Component Pin-out Configuration" section.

# SHIPPING CONSIDERATIONS

The board will withstand the following vibrations without any detrimental effects to its operation or life expectancy:

Frequency 7 to 100 HZForce 7 to 100 HZ1.2 G's, minimum

Time 2.5 hours

Shock 30 G's in any plane with no surrounding protective package.

# REFERENCES

- Intel Corporation:

- Microsystem Components, volumes I and II

- Memory Components Handbook

- Microprocessor and Peripheral Handbook

- Introduction to the iAPX 286

- iAPX 286 Hardware Reference Manual

- iAPX 286 Programmer's Reference Manual

- iAPX 286 Operating Systems Writer's Guide

- Texas Instruments:

- MOS Memory Supplement

- · Motorola, Incorporated

- Microprocessors Data Manual

Contents

# Functional Description

| PROCESSOR BOARD2                            |

|---------------------------------------------|

| 80286 Microprocessor                        |

| Random Access Memory (RAM)                  |

| RAM Memory Reset Timing (PFR)               |

| Reset Generation (PFR)                      |

| Read Only Memory (ROM)2-                    |

| Direct Memory Access (DMA)2-                |

| Timer/Counter2-1                            |

| Interrupt Control 2-1                       |

| Numeric Processor Extension                 |

| CPU VLSI2-1                                 |

| DRAM Controller VLSI —                      |

| Power Fail Recovery Board (PFR)2-1          |

| DRAM Controller VLSI —                      |

| Non-Power Fail Recovery Board (NPFR)2-1     |

| Real-Time Clock VLSI 2-1                    |

| Input and Output Control Line Functions 2-1 |

| Multiplexed Bidirectional Address/Data Bus  |

| ALE - Multiplexed Address Strobe 2-19       |

| IRQ - Interrupt Request2-2                  |

| RESET2-20                                   |

| PS - Power Sense                            |

| Address Map2-20                             |

| Periodic Interrupt Selection2-22            |

| Alarm Interrupt Selection 2-29              |

| Static CMOS RAM2-23                         |

| Update Cycle2-24                            |

| RTC Registers2-25                           |

| Register A 2-25                             |

| Update In Progress Bit 2-26                 |

| Rate Selection Bits                         |

| Register B                                  |

# The Core Memory Project Periodic Interrupt Enable Bit ......2-27 Alarm Interrupt Enable Bit......2-27 Update-ended Interrupt Enable Bit......2-27 Daylight Savings Enable Bit ......2-28 Register C......2-28 Periodic Interrupt Flag ......2-28 Alarm Interrupt Flag......2-28 Update-Ended Interrupt Flag .......2-29 Register D ......2-29 Valid RAM and Time Bit ......2-29 Keyboard Interface ......2-30 Address Maps ......2-32 Memory Address Map......2-32 1/O Address Map ......2-34 CONNECTORS ......2-36 Battery Connector ......2-36 Keyboard/Power Good Connector ......2-37 Logic Signals and Their Functions .......2-41

# Functional Description

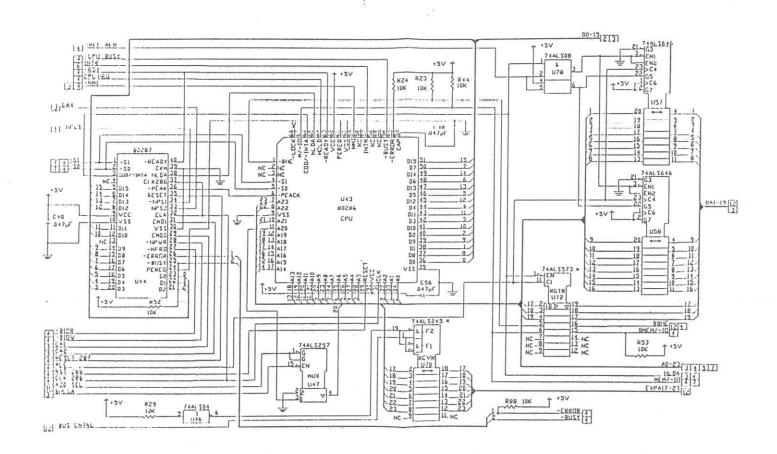

#### PROCESSOR BOARD

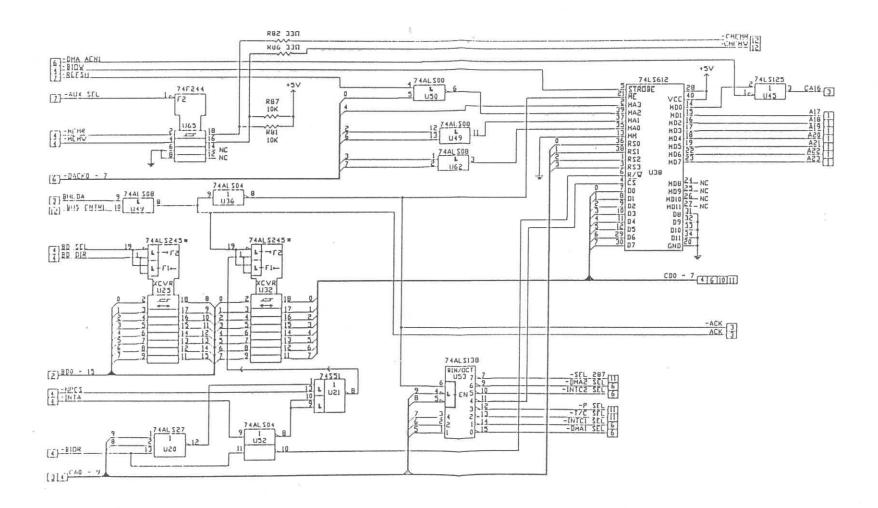

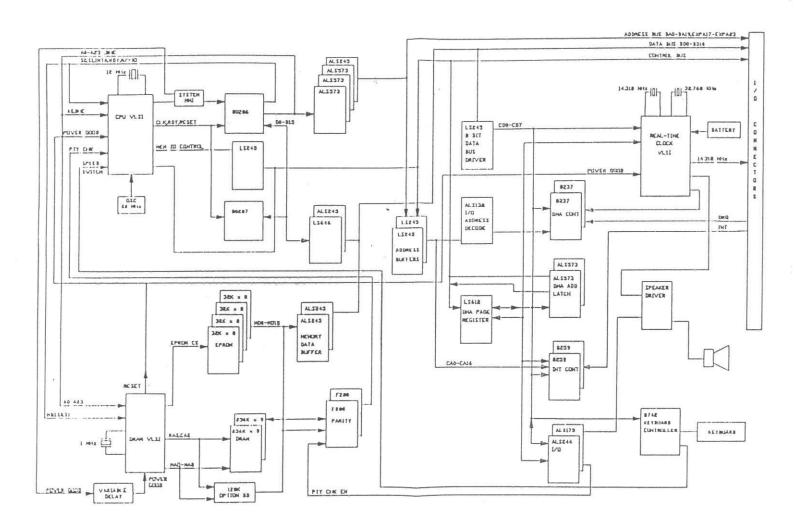

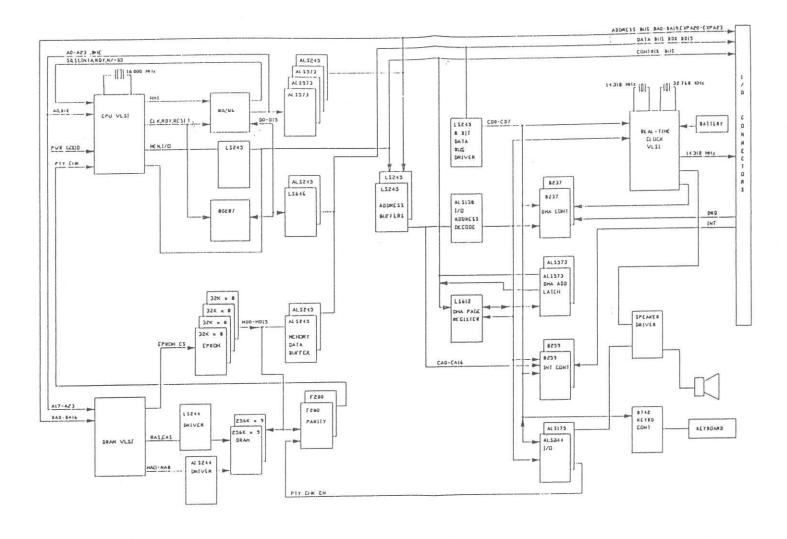

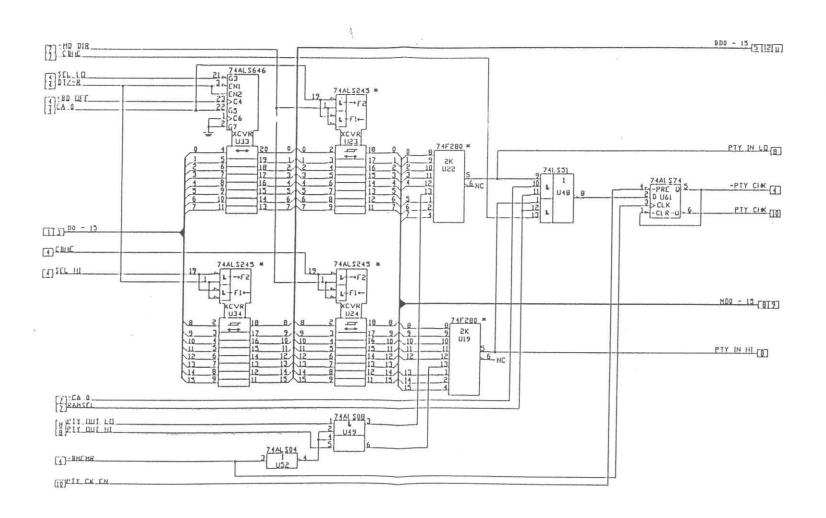

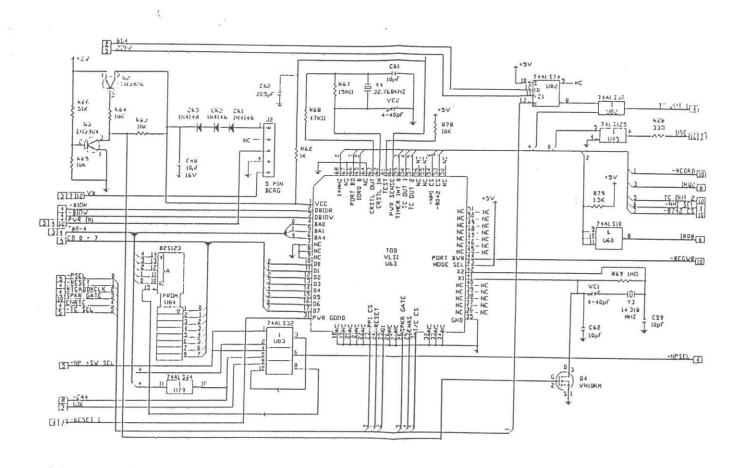

This section contains a functional description of the processor board. The major functions, as shown in Figure 2-4, described are:

- 80286 Microprocessor control

- DRAM VLSI control

- CPU VLSI control

- Real-Time Clock VLSI control

- DMA control

- Interrupt control

- 80287 Numeric Processor control

- Keyboard control

- ROM control

- RAM control

- Addressing

- Connector signal control

#### 80286 MICROPROCESSOR

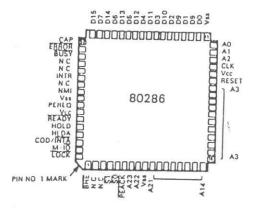

The central processing unit (U43) is an INTEL 80286-10. It has a clock rate of 6.0MHz, 8.0MHz, or 10.0MHz. The clock rate may be selected through the DOS FREQ utility or the keyboard by pressing ALT, ESC, and SYS REQ simultaneously. Proper jumper strapping is required for the selected speed; refer to the Switches, Jumpers, and Adjustments chapter of this manual.

Two upwardly compatible operating modes are supported: the real address mode and the protected virtual address mode. The real address mode of the 80286 allows a 1 MB address space. In protected mode, a 16 MB real address space with 1 GB virtual addressing per task is supported.

The processor board also supports an 80287 high performance 80-bit math coprocessor.

A comparison of overall system performance showing wait states and cycle times for the different operating speeds is shown in Figure 2-1.

| CYCLE<br>TYPE           | CPU<br>CLOCK<br>CYCLE | WAIT<br>STATE | 6 MHz<br>CYCLE<br>TIME | 8 MI Iz<br>CYCLE<br>TIME | 10 MHz<br>CYCLE<br>TIME | 8 MHz<br>0 MEMORY<br>WAIT STATES |

|-------------------------|-----------------------|---------------|------------------------|--------------------------|-------------------------|----------------------------------|

| 16 BIT BUS              | 2 2                   | 1 0           | 500ns                  | 375ns                    | 300ns                   | 250ns BASE<br>250ns MEMORY       |

| 16 BIT BUS              | 2 2                   | 1 2           | 500ns                  | 375ns                    | 400ns                   | 375ns EXPANSION<br>375ns MEMORY  |

| 8 BIT TO<br>8 BIT I/O   | 2                     | 4 6           | 1000ns                 | 750ns                    | 800ns                   | 750ns                            |

| 16 BIT TO<br>8 BIT I/O  | 2                     | 10<br>14      | 2000ns                 | 1500ns                   | 1600ns                  | 1500ns                           |

| 16 BIT TO<br>16 BIT I/O | 2                     | 1 2           | 500ns                  | 375ns                    | 400ns                   | 375ns                            |

Figure 2-1 System performance

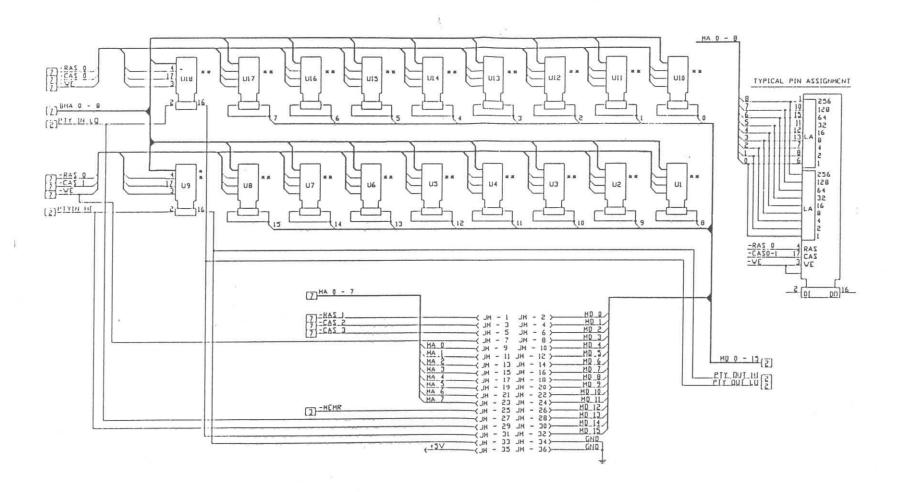

The processor board has two banks, 512K bytes, of dynamic RAM (U1-U18). Each bank consists of eight chips for data and one for parity checking.

RAM memory may be increased to a maximum of 640K bytes by inserting a 128K expansion board into one of the expansion slots or by using the 128K expansion connector (JM1) on the processor board with the 128K piggyback board. Additional memory may be added in the form of RAM expansion cards.

The dynamic RAM memory is refreshed using the DRAM VLSI, the CPU VLSI and counter 1 of the timer. Refresh requires one memory cycle every 15 microseconds. In power-down operation, a strap allows the memory to be refreshed at a slower rate, to conserve power.

Single bit errors are detected using a ninth bit for parity. A parity error generates a non-maskable interrupt to the 80286 CPU.

#### 80286 MICROPROCESSOR

The central processing unit (U43) is an INTEL 80286-10. It has a clock rate of 6.0MHz, 8.0MHz, or 10.0MHz. The clock rate may be selected through the DOS FREQ utility or the keyboard by pressing ALT, ESC, and SYS REQ simultaneously. Proper jumper strapping is required for the selected speed; refer to the Switches, Jumpers, and Adjustments chapter of this manual.

Two upwardly compatible operating modes are supported: the real address mode and the protected virtual address mode. The real address mode of the 80286 allows a 1 MB address space. In protected mode, a 16 MB real address space with 1 GB virtual addressing per task is supported.

The processor board also supports an 80287 high performance 80-bit math coprocessor.

A comparison of overall system performance showing wait states and cycle times for the different operating speeds is shown in Figure 2-1.

| CYCLE<br>TYPE           | CPU<br>CLOCK<br>CYCLE | WAIT<br>STATE | 6 MHz<br>CYCLE<br>TIME | 8 MHz<br>CYCLE<br>TIME | 10 MHz<br>CYCLE<br>TIME | 8 MHz<br>0 MEMORY<br>WAIT STATES |

|-------------------------|-----------------------|---------------|------------------------|------------------------|-------------------------|----------------------------------|

| 16 BIT BUS              | 2 2                   | 1 0           | 500ns                  | 375ns                  | 300ns                   | 250ns BASE<br>250ns MEMORY       |

| 16 BIT BUS              | 2 2                   | 1 2           | 500ns                  | 375ns                  | 400ns                   | 375ns EXPANSION<br>375ns MEMORY  |

| 8 BIT TO<br>8 BIT I/O   | 2                     | 4 6           | 1000ns                 | 750ns                  | 800ns                   | 750ns                            |

| 16 BIT TO<br>8 BIT I/O  | 2                     | 10<br>14      | 2000ns                 | 1500ns                 | 1600ns                  | 1500ns                           |

| 16 BIT TO<br>16 BIT I/O | 2                     | 1 2           | 500ns                  | 375ns                  | 400ns                   | 375ns                            |

Figure 2-1 System performance

The processor board has two banks, 512K bytes, of dynamic RAM (U1-U18). Each bank consists of eight chips for data and one for parity checking.

RAM memory may be increased to a maximum of 640K bytes by inserting a 128K expansion board into one of the expansion slots or by using the 128K expansion connector (JM1) on the processor board with the 128K piggyback board. Additional memory may be added in the form of RAM expansion cards.

The dynamic RAM memory is refreshed using the DRAM VLSI, the CPU VLSI and counter 1 of the timer. Refresh requires one memory cycle every 15 microseconds. In power-down operation, a strap allows the memory to be refreshed at a slower rate, to conserve power.

Single bit errors are detected using a ninth bit for parity. A parity error generates a non-maskable interrupt to the 80286 CPU.

# READ ONLY MEMORY (ROM)

The processor board has four sockets, U27 - U30, for ROM or erasable-programmable-read-only memory (EPROM). Each socket accommodates 27128 (16k x 8) or 27256 (32k x 8) memory chips. Refer to Figures 1-1 or 1-2 for the location of the four ROM/EPROM sockets.

The top 64K of memory, F0000(11) to FFFFFF(II) real mode (1M total system memory), and FF0000(II) to FFFFFF(II) protected mode (16M total system memory) are reserved for ROM BIOS. The address map for the ROMs is shown in Figure 2-3. At 6.0 MHz a ROM memory cycle is 375ns and the data access time is 200ns. With the 10 MHz option enabled ROM memory cycles are 300ns and data access time is 180ns.

| ADDRESS          | DEVICE DESIGNATION        |

|------------------|---------------------------|

| 0E0000 TO 0EFFFF | Reserved ROM memory space |

| 0F0000 TO 0FFFFF | BIOS ROM memory space     |

| FE0000 TO FEFFFF | Reserved ROM memory space |

| FF0000 TO FFFFFF | BIOS ROM memory space     |

Figure 2-3 ROM address map

Figure 2-4 Power fail recovery board functional block diagram (PFR)

X

gure 2-5 Non-power fail recovery board functional block diagram (NPFR)

# DIRECT MEMORY ACCESS (DMA)

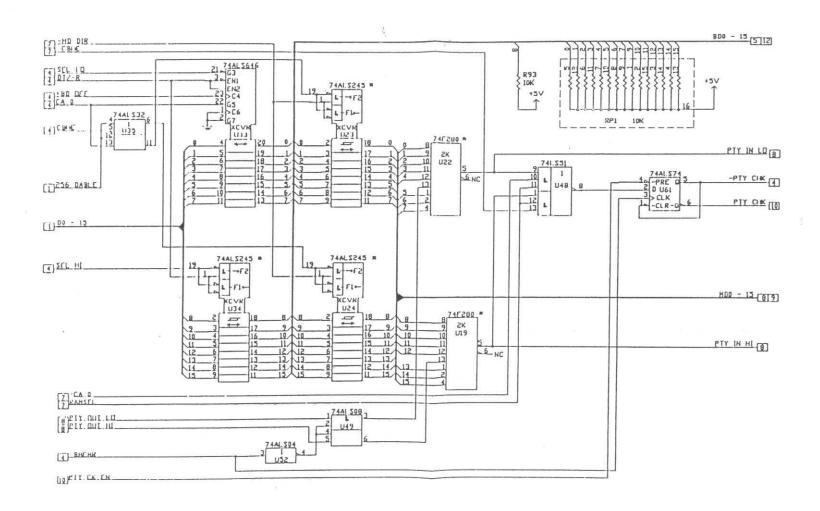

The processor board includes two INTEL 8237-5 DMA controllers, (U55 and U66). Each controller has four channels. Since one channel is used for cascading, seven are available for system use.

DMA controller 1 (U55) controls channels 0-3. It supports 8-bit data transfers between 8-bit I/O devices and 8-bit or 16-bit system memory. Data is transferred in blocks up to 64K bits in size and can be transferred anywhere in the total system memory address range of 16M bytes. DMA controller 1 controls addresses A0 to A15 and its associated page register controls A16 to A23.

DMA controller 2 (U66) controls channels 4-7. It supports 16-bit data transfers between 16-bit I/O devices and 16-bit memory. Data is transferred, in blocks up to 128K bits in size, on even byte boundaries only. Channel 4 is reserved for cascading the two controllers. DMA controller 2 controls address lines A1 to A16 and its associated page register controls lines A17 to A24.

DMA page register (U38), for channels 5-7, contain the address bits A17 through A23. The addresses are output in data bits D1 through D7. D0 is not used for 16-bit transfers. The base address, for channels 5-7, written into the base address register should be the real address divided by two.

When addressing memory DMA channel addresses, do not increment across page boundaries.

The Page Register addresses are shown in Figure 2-6.

| DMA<br>CONTROLLER | CHANNEL | FUNCTION         | PAGE REGISTER<br>I/O ADDRESS |       |

|-------------------|---------|------------------|------------------------------|-------|

| 1                 | 0       | UNDEDICATED      | 8711                         | MILIF |

| 1                 | 1       | SDLC             | 83H                          | 00    |

| 1                 | 2       | FLEX DISK        | 8114                         |       |

| 1                 | 3/      | UNDEDICATED      | 82H:                         |       |

| 2                 | 4       | CASCADE TO CNT 1 |                              |       |

| 2                 | 5       | UNDEDICATED      | 8BH                          | (O-D) |

| 2                 | 6       | UNDEDICATED      | 89H                          | CO-D1 |

| 2                 | 7       | UNDEDICATED      | 8AH                          |       |

|                   |         | REFRESH REGISTER | 8FH                          |       |

|                   |         |                  |                              |       |

Figure 2-6 Page register addresses

The DMA controller command code addresses are shown in Figure 2-7.

| ADDRESS | FUNCTION                             |

|---------|--------------------------------------|

| 00011   | CH0 BASE AND CURRENT ADDRESS         |

| 0C2H    | CHO BASE AND CURRENT WORD COUNT      |

| 0C4H    | CHI BASE AND CURRENT ADDRESS         |

| 0C6H    | CH1 BASE AND CURRENT WORD COUNT      |

| · 0C8H  | CH2 BASE AND CURRENT ADDRESS         |

| OCAH    | CH2 BASE AND CURRENT WORD COUNT      |

| OCCH    | CH3 BASE AND CURRENT ADDRESS         |

| 0CEH    | CH3 BASE AND CURRENT WORD COUNT      |

| 0D0H    | READ STATUS REG OR WRITE COMMAND REG |

| 0D2H    | WRITE REQUEST REGISTER               |

| 0D4H    | WRITE MASK REGISTER (SINGLE BIT)     |

| ODGH    | WRITE MODE REGISTER                  |

| OD8H    | CLEAR BYTE POINTER                   |

| 0DAH    | READ TEMP REGISTER OR MASTER CLEAR   |

| OUCH    | CLEAR MASK REGISTER                  |

| ODEH    | WRITE MASK REGISTER (ALL BITS)       |

Figure 2-7 DMA controller command code addresses

# TIMER/COUNTER

The board provides three programmable 16-bit timer counters (U63). Counter 0 is tied to interrupt 0, counter 1 is used for dynamic RAM refresh and counter 2 is used for the speaker, as shown in Figure 2-8.

| COUNTER | CLK IN   | OUTPUT          |

|---------|----------|-----------------|

| 0       | 1.190MHz | 8259A IRQ0      |

| 1       | 1.190MHz | REFRESH REQUEST |

| 2       | 1.190MHz | SPEAKER DRIVE   |

Figure 2-8 Timer counters

# INTERRUPT CONTROL

Two 8259A-2 interrupt controllers (U67 and U68 for the PFR board and U68 and U69 for the NPFR board) regulate the interrupt requests from external devices. They are cascaded to provide 16 levels of interrupts as shown in Figure 2-9.

| Interrupt |                | Use                                     |

|-----------|----------------|-----------------------------------------|

| (U68)     | 0              | Timer Counter 0                         |

|           | 1              | Keyboard output buffer full             |

| 20-31=1   | <del>→</del> 2 | Cascade input from second controller    |

| X0-01-    | 3              | Auxiliary serial port                   |

|           | 4              | Serial Asynchronous Communications Port |

|           | 5              | Auxiliary parallel port                 |

|           | 6              | Flex disk drive controller              |

|           | 7              | Parallel (Printer) Port                 |

| (U67)     | 8              | Clock Interrupt                         |

|           | 9              | Causes IRQ2 (software controlled)       |

| 1         | 10             | Reserved                                |

| 10-BF     | 11             | Reserved                                |

| o pr      | 12             | Reserved                                |

|           | 13             | 80287 Coprocessor                       |

|           | 14             | Fixed disk drive controller             |

|           | 15             | Reserved                                |

Figure 2-9 Hardware interrupt assignments

A non-maskable interrupt (NMI) is activated when either:

- A parity error occurs when reading from RAM

- An error has occurred in a device in one of the expansion slots

- Power to the power supply has been lost. (Applicable only to the PFR board.)

# NUMERIC PROCESSOR EXTENSION

This board supports an 80287 high performance numeric processor (U44) which provides high-speed mathematical computation capabilities. The specific device speed required depends on the operational speed of the system, as shown in Figure 2-10.

| SYSTEM CLOCK | COPROCESSOR TYPE REQUIRED |

|--------------|---------------------------|

| 6.0 MHz      | 80287-3                   |

| 8.0 MHz      | 80287-8                   |

| 10.0 MHz     | 80287-8                   |

Figure 2-10 System speed/coprocessor type requirements

The numeric processor control registers function as follows:

An OUT instruction to port 0F0H clears the 80287 busy signal.

This busy signal is latched if the 80287 generates an error signal while busy.

An OUT instruction to port 0F1II resets the 80287.

When the processor board is powered up, the non-maskable interrupt (NMI) is disabled outside the 80286.

Enable the NMI by writing a byte with data bit 7 equal to a logic 1, to I/O address 070H.

Disable the NMI by writing a byte with data bit 7 equal to a logic 0, to I/O address 070H

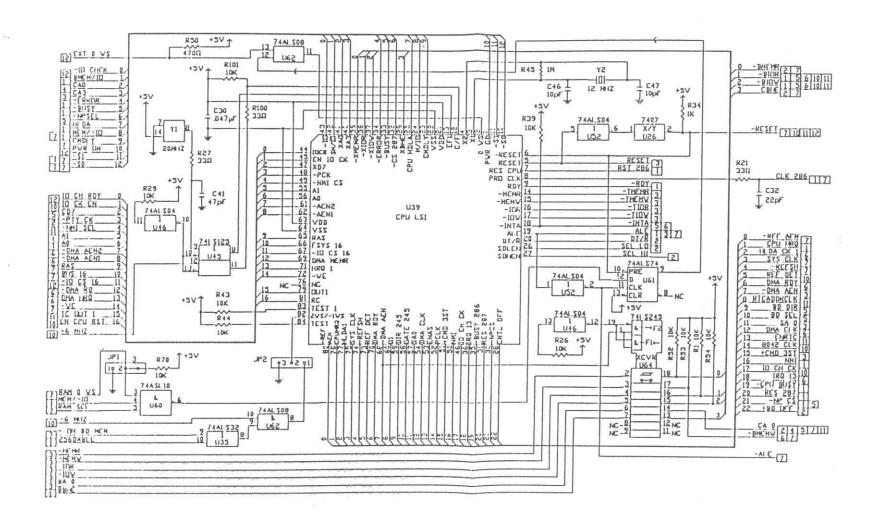

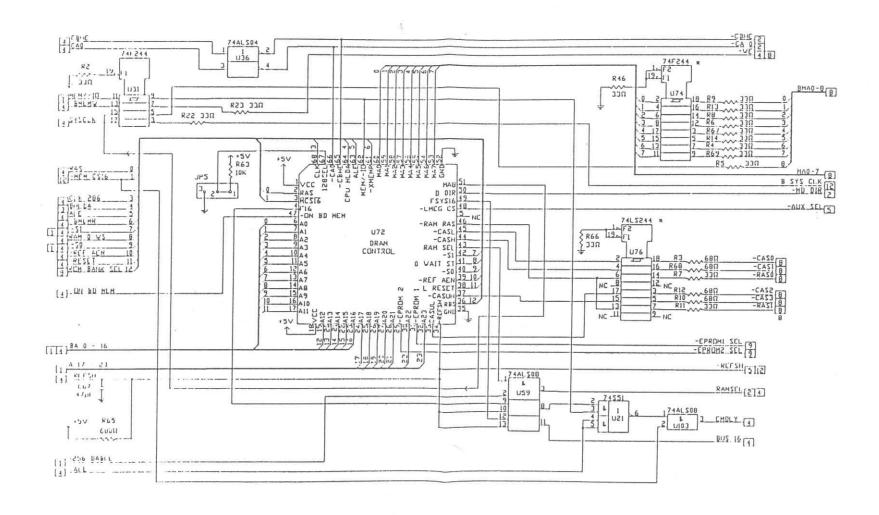

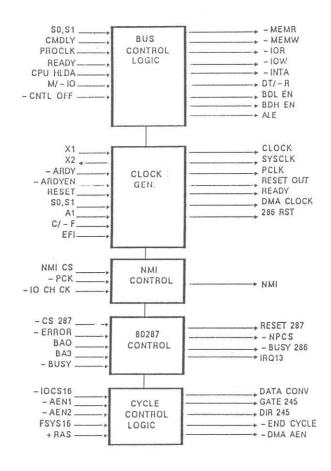

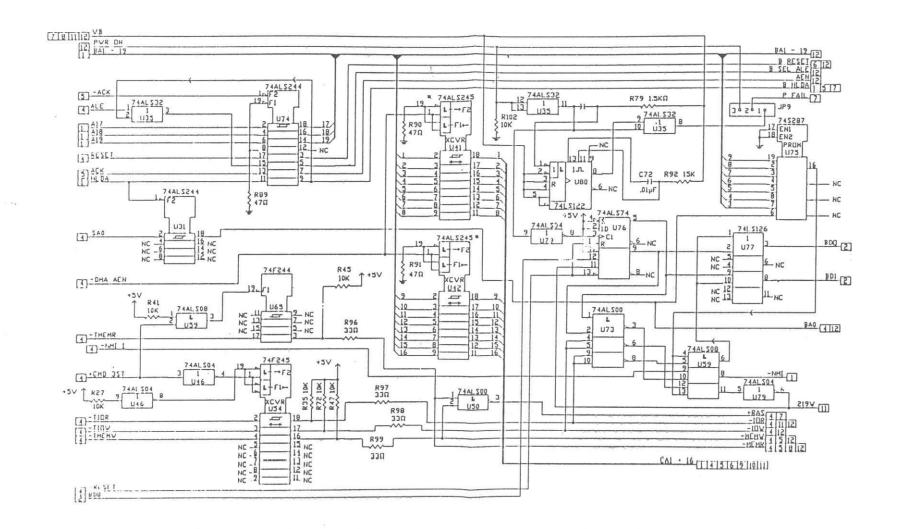

## CPU VLSI

The CPU VLSI, U39, is a CMOS chip containing much of the 'glue' logic required for operation of the processor board. The main features of this chip are system clock generation, system control signal generation, shut down logic and NMI control logic. The device is packaged in a 84-pin plastic leaded chip carrier (PLCC). Figure 2-11 is a block diagram of the CPU VLSI chip.

Figure 2-11 CPU VLSI block diagram

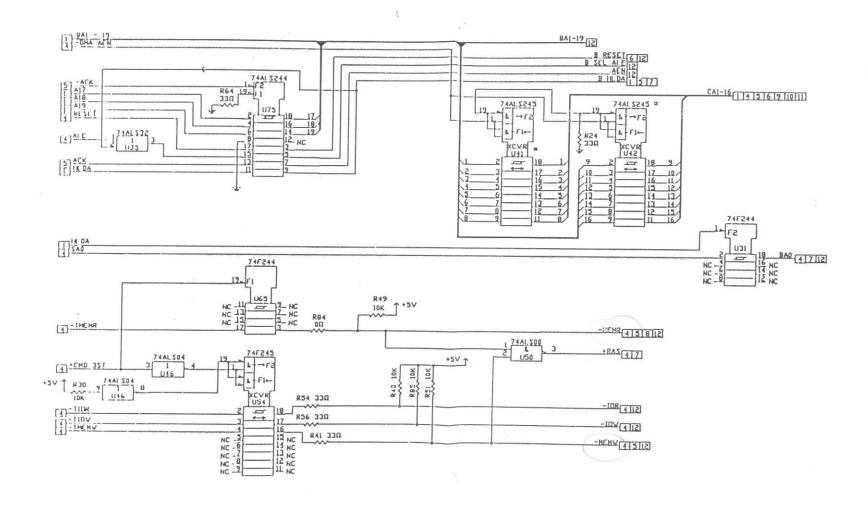

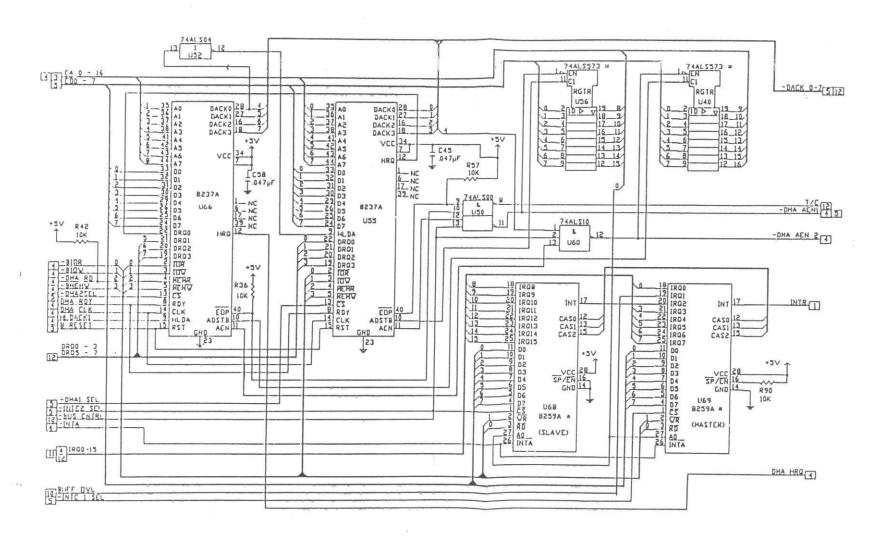

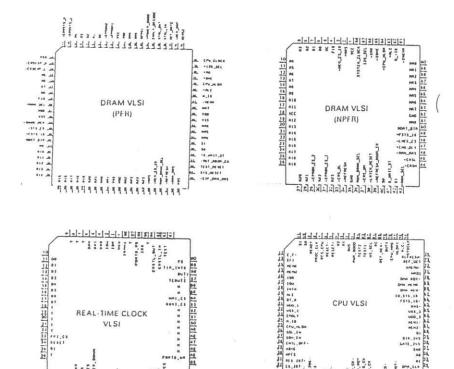

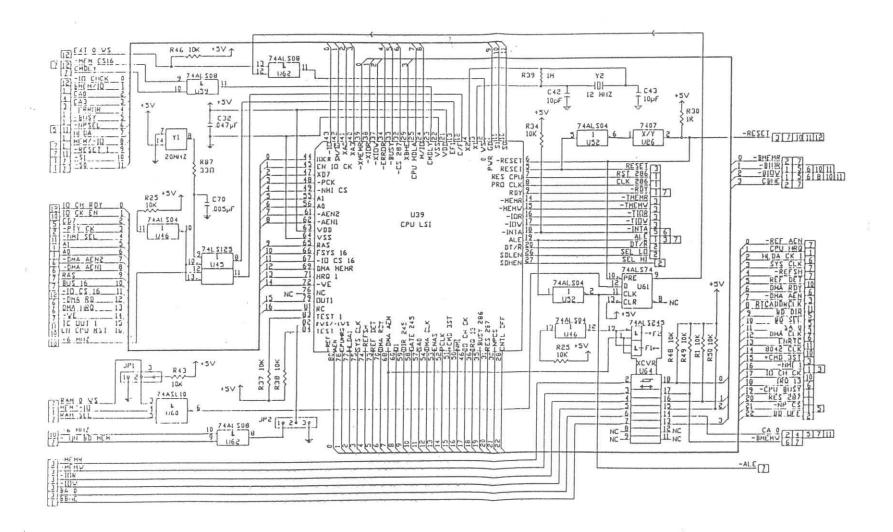

# DRAM CONTROLLER VLSI -POWER FAIL RECOVERY BOARD (PFR)

The DRAM controller VLSI chip (U71) generates the appropriate signals required to control up to 2.128M bytes of dynamic RAM and 128K bytes of EPROM/ROM, and maintain the RAM when in the power down mode. The length of time that the integrity of memory can be maintained depends on the amount of memory and the size of the battery. The DRAM controller is packaged in a 84-pin PLCC. Figure 2-12 is a block diagram of the DRAM controller.

NOTE: This information applies only to the power fail recovery board.

Figure 2-12 DRAM controller VLSI (PFR)

Signals MEMS1, MEMS2, -MEM\_MAP, and 128\_SEL decode the addresses on the chip. If the address is a RAM address, the proper RAS and CAS signals are generated. If the ADVANCE\_DECODE signal is held high, the chip allows 0 wait state operation. If the ADVANCE\_DECODE function is active, signals M/-IO, S0, and S1 determine if the current machine cycle is a memory read or a memory write. If the ADVANCE\_DECODE function is not active, the chip waits for the +RAS signal to go high before generating RAS and CAS signals to memory. No advance decoding is possible during a DMA cycle.

Under normal operation, this chip generates a refresh RAS once every 15 microseconds. After power is lost, the chip runs through a normal refresh for 512 cycles. Memory is then refreshed at an extended rate, if jumper JP6 is set to 1-2, which is about eight times slower than normal memory speed. Upon power-up, the chip reverts back to the normal refresh rate and begins normal operation. The ROM BIOS firmware is responsible for keeping -REFRESH high long enough for 512 refresh cycles to be generated before -REFRESH goes low.

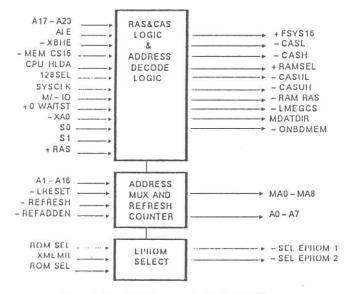

# DRAM CONTROLLER VLSI -NON-POWER FAIL RECOVERY BOARD (NPFR)

The DRAM controller VLSI (U72) generates the appropriate signals required to control up to 640K bytes of dynamic RAM and 128K bytes of EPROM/ROM. The DRAM controller is packaged in a 68 pin PLCC. Figure 2-13 is a block diagram of the DRAM controller.

NOTE: This information applies only to the non-power fail recovery, board.

Figure 2-13 DRAM controller VLSI (NPFR)

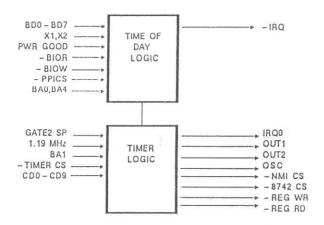

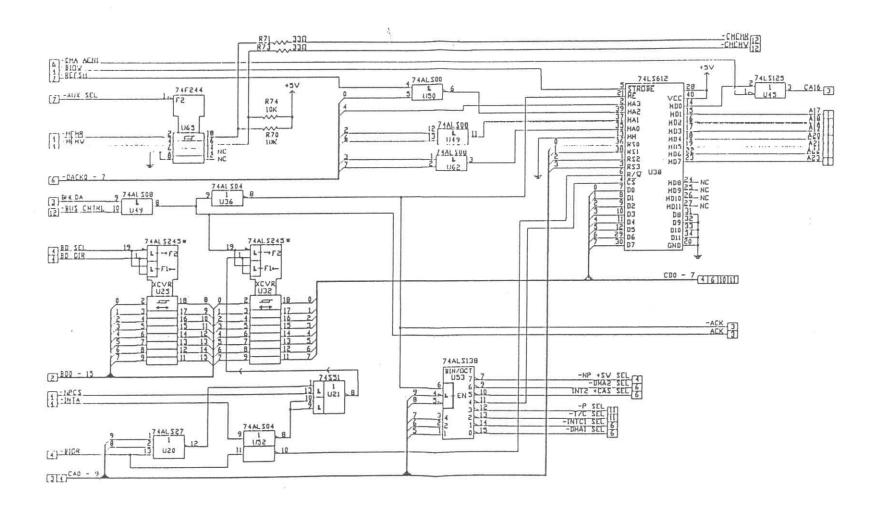

#### REAL-TIME CLOCK VLSI

The Real-Time Clock (RTC) VLSI chip, U63, contains the functional equivalent of the Motorola MC146818 Time of Day chip and the Intel 8254 Timer chip. It supports all of the time of day modes provided by the MC146818, three user programable counters, and battery back-up. The chip is packaged in a 68-pin PLCC. Figure 2-14 is a block diagram of the RTC VLSI chip. This section includes a block diagram, an I/O address map, a list of significant features of the chip, and a description of the interface to the chip.

Figure 2-14 RTC VLSI block diagram

The real-time clock logic contains 14 bytes used by the RTC chip for time and date control. The remaining 50 bytes are used by the processor board to store various parameters required for system operation. The function of each of these bytes is outlined in Figure 2-15.

| I/O ADDRESS | FUNCTION                      |

|-------------|-------------------------------|

| 0011        | RTC Seconds*                  |

| 0111        | RTC Seconds alarm*            |

| 02H         | RTC Minutes*                  |

| 03H         | RTC Minutes alarm*            |

| 04H         | RTC Hours*                    |

| 05H         | RTC Hours alarm*              |

| 06H         | RTC Day of the week*          |

| 0711        | RTC Day of the month          |

| H80         | RTC Month                     |

| 0911        | RTC Year                      |

| 0AH         | RTC Status register A         |

| 0BH         | RTC Status register B         |

| OCH         | RTC Status register C         |

| 0DH         | RTC Status register D         |

| OEH         | Status byte (Diagnostic)*     |

| OFH         | Status byte (Shutdown)*       |

| 1011        | Flex disk drive (Type)        |

| 11H         | Unused                        |

| 12H         | Fixed disk drive (type)       |

| 13H         | Unused                        |

| 14H         | Equipment flag                |

| 15H         | Base memory byte (Low)        |

| 1611        | Base memory byte (High)       |

| 17H         | Expansion memory byte (Low)   |

| 1811        | Expansion memory byte (High)  |

| 19H-2DH     | Unused -                      |

| 2EH-2FH     | Checksum                      |

| 30H         | Expansion memory byte (Low)*  |

| 3111        | Expansion memory byte (High)* |

| 32H         | Century data*                 |

| 33H         | Power on Flags*               |

| 34H-3FH     | Unused                        |

<sup>\*</sup> These bytes are not included in the checksum calculation.

Figure 2-15 RTC RAM I/O address map

The following is a list of significant features of the RTC VLSI chip:

- o Internal Time Base and Oscillator

- o Counts Seconds, Minutes, and Hours of the Day

- e Counts Days of the Week, Date, Month, and Year

- © Time Base Input: 32.768 KHz

70-7F

- Time Base Oscillator for Parallel Resonant Crystals

- o Binary or BCD Representation of Time, Calendar, and Alarm

- o 12 or 24 Hour Clock with AM and PM in 12 Hour Mode

- o Automatic End of Month Recognition

- o Automatic Leap Year Compensation

- o Interfaced as 64 RAM Locations

- 14 Bytes of Clock and Control Registers

- o 50 Bytes of General Purpose RAM

- Status Bit Indicates Data Integrity

- Three software-maskable and testable interrupts:

- Time of Day Alarm, Once-per-Second to Once-per-Day

- Periodic Interrupt Rates from 122.070 uS to 500 mS

- End-of-Clock Update Cycle

The interface to the RTC is described below.

# input and Output Control Line Functions

The functions of the I/O control lines are described below.

Multiplexed Bidirectional Address/Data Bus (AD0-AD7) -- The bus presents the address during the first phase of the bus cycle, and the data during the second phase. The valid address must be presented just before the fall of ALE. Valid write data must be presented and held stable at the end of the write cycle. In a read cycle, 8 bits of data are output near the end of the cycle.

ALE - Multiplexed Address Strobe -- This input is a positive strobe pulse that demultiplexes the bus. The falling edge of ALE causes the address to be latched within this device.

IRQ - Interrupt Request -- This active High output interrupts the host processor as needed. The IRQ output remains High as long as the status bit enabling the interrupt is set. To clear IRQ, the processor reads Register C. RESET also clears pending interrupts. When no interrupt is occurring, the IRQ pin is Low or Tri-Stated according to the way the RTC is programmed.

RESET -- This input does not affect the clock, calendar, or RAM functions. It does affect the following:

- Periodic Interrupt Enable (PIE) bit is cleared, zero

- Alarm Interrupt Enable (AIE) bit is cleared, zero

- Update Ended Interrupt Enable (UIE) bit is cleared, zero

- Update Ended Interrupt Flag (UF) bit is cleared, zero

- Interrupt Request Status Flag (IRQF) bit is cleared, zero

- · Periodic Interrupt Flag (PF) bit is cleared, zero

- · Alarm Interrupt Flag (AF) bit is cleared, zero

- IRQ pin is Tri-Stated

PS - Power Sense -- This input controls the Valid RAM and Time (VRT) bit in Status Register D. When PS is low, the VRT bit is cleared. During power-up, the PS pin must be externally held low for a minimum of 5uS. As power is applied, the VRT bit remains LOW. The contents of RAM, time registers, and calendar are not guaranteed as long as the VRT bit is low.

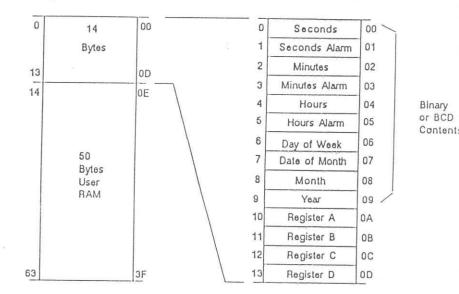

Address Map -- Memory consists of 50 user RAM bytes, 10 time, calendar, and alarm data bytes, and four control and status bytes. The processor can read and write to all 64 bytes except registers C and D, Bit 7 of Register A and of the seconds byte, which are read only, and Bit 7 of the seconds byte which is always "0". Figure 2-16 shows the RAM address map and control registers in this chip.

The processor obtains time and calendar information by reading the proper locations. The time, calendar, and alarm may be initialized by writing to the correct RAM locations. The contents of the ten time, calendar, and alarm bytes can be either binary or binary coded decimal (BCD). Figure 2-17 shows the binary and BCD formats of the ten time, calendar, and alarm locations.

Figure 2-16 RAM and control registers address map

| Aukkess  |                                              | Decarnal Range |                                          |                                          | Example*            |          |

|----------|----------------------------------------------|----------------|------------------------------------------|------------------------------------------|---------------------|----------|

| Location |                                              | Range          | Briary Data Mode                         | BCD Data Mode                            | Benary<br>Data Mode | Data Mod |

| 0        | Seconds                                      | 0 - 59         | \$00 - \$38                              | \$00 - \$59                              | 15                  | 21       |

| 1        | Seconds Alarm                                | 0 - 59         | \$00 - \$38                              | \$00 - \$69                              | 15                  | 21       |

| 2        | Minutes                                      | 0 - 69         | \$00 - \$3B                              | \$00 - \$58                              | 34                  | 54       |

| 3        | Minutes Alarm                                | 0 - 59         | \$00 - \$38                              | 800 - \$69                               | 34                  | 6.8      |

|          | Hines Alarm<br>(12 Hone Mode)                | 1 - 12         | \$01 - \$0C (AM) and<br>\$81 - \$8C (PM) | 801 - 812 (AM) and<br>881 - 802 (PM)     | 06                  | 06       |

| 4        | (24 Phra Mude)                               | 0 - 23         | \$00 - \$17                              | \$00 - \$23                              | 05                  | 0.5      |

| 6        | Hours Alarm<br>(12 Hour Mide)<br>Hours Alarm | 1 - 12         | \$01 - \$0C (AM) and<br>\$81 - \$8C (PM) | \$01 - \$12 (AM) and<br>\$81 - \$92 (PM) | 05                  | 05       |

|          | (24 Hour Mode)                               | 0 - 23         | 800 - 817                                | \$00 - \$23                              | 0.5                 | 0.5      |

| 0        | Day of Big Wook<br>Sisting - 1               | 1 - 7          | 801 - 807                                | 801 - 607                                | 0.6                 | 06       |

| 7        | Date of the Mariti                           | 1 - 21         | 801 - 81/                                | 801 - 831                                | OF                  | 16       |

|          | Month                                        | 1 - 12         | \$01 - \$0C                              | \$01 - \$12                              | 02                  | 02       |

| 9        | Year                                         | 0 - 99         | 500 - 563                                | \$00 - \$99                              | 45                  | 7.9      |

Figure 2-17 Time, calendar, and alarm data modes

Periodic Interrupt Selection -- The periodic interrupt allows the IRQ pin to be triggered once every 122.070 uS to 500mS. It is separate from the alarm interrupt which can output once per second to once per day. Figure 2-18 shows the selection of the Register A bits that set the periodic interrupt frequency. The periodic interrupts must be enabled by the PIE bit in Register B.

| Rate Select<br>Control Register A<br>RS3 RS2 RS1 RS0 |     | ol Register A Periodic Interrupt |     | Rate Select<br>Control Register A<br>RS3 RS2 RS1 RS0 |     |     |     | 32.768 KHz Time Base<br>Periodic Interrupt |            |

|------------------------------------------------------|-----|----------------------------------|-----|------------------------------------------------------|-----|-----|-----|--------------------------------------------|------------|

| RS3                                                  | RS2 | RS1                              | RS0 | Rate tPI                                             | RS3 | RS2 | RS1 | RSO                                        | Rate tPI   |

| U                                                    | O   | U                                | 0   | None                                                 | 1   | 0   | 0   | 0                                          | 3.90625 mS |

| 0                                                    | 0   | 0                                | 1   | 3.90625 mS                                           | 1   | 0   | 0   | 1                                          | 7.8125 mS  |

| 0                                                    | 0   | 1                                | 0   | 7.8125 mS                                            | 1   | 0   | 1   | 0                                          | 15.625 mS  |

| 0                                                    | 0   | 1                                | 1   | 122.070 uS                                           | 1   | 0   | 1   | 1                                          | 31.25 mS   |

| 0                                                    | 1   | 0                                | 0   | 244.141 uS                                           | 1   | 1   | 0   | 0                                          | 62.5 mS    |

| 0                                                    | 1   | 0                                | 1   | 488.281 uS                                           | 1   | 1   | 0   | 1                                          | 125 mS     |

| 0                                                    | 1   | 1                                | 0   | 976.562 uS                                           | 1   | 1   | 1   | 0                                          | 250 mS     |

| 0                                                    | 1   | 1                                | 1   | 1.953125 mS                                          | 1   | 1   | 1   | 1                                          | 500 mS     |

Figure 2-18 Register A rate selection bit settings

Alarm Interrupt Selection -- The three alarm bytes can be used in two ways. The processor can insert an alarm time in the appropriate hours, minutes, and seconds alarm locations and set the alarm enable bit to enable the alarm interrupt to occur at the specified time each day.

A "Don't Care" ("DC") code can also be inserted in any of the three alarm bytes to obtain different results. A "DC" code is any hexadecimal byte, from C0 to FF, with its two most significant bits set to 1. An alarm interrupt occurs each hour if a "DC" is inserted in the hours alarm byte, each minute if inserted in the hours and minutes bytes, or each second if inserted into all three alarm bytes.

The processor selects which interrupts, if any, it wishes to receive. A "1" written to the appropriate register B bit locations enables one of the three interrupts. A "0" in a bit location prohibits the corresponding interrupt from occurring. If an interrupt flag is already set when the interrupt is enabled, the IRQ pin is immediately activated though the interrupt, that initiated the event, may have occurred much earlier. Therefore, the processor should clear earlier initiated interrupts before enabling new interrupts. When an interrupt occurs, a flag bit is set to a "1" in Register A. Each of the interrupts have a bit in Register A which are set independent of the state of the corresponding enable bits in Register B. The flags may be used with or without enabling the corresponding enable bits. However, there is one precaution: the flag bits in Register A are cleared when Register A is read, more than one interrupt bit could be set in a read and all would be erased. Therefore, if the processor is polling instead of using interrupts, all set bits should be read and the bit status saved while handling all polled interrupts.

Static CMOS RAM -- The 50 bytes of RAM are not dedicated to any particular function. They may be used by the processor and are accessible during the update cycle. They can be used to store essential non-volatile data since the RAM can be kept valid by use of battery backup.

Update Cycle -- The RTC executes an update cycle once per second assuming one of the proper time bases is in place and the SET bit in Register B is clear. When the SET bit is a "1", the processor can initialize the time and calendar bits by stopping any existing update and by preventing a new one to begin. The most important function of the update cycle is to increment the seconds byte, check for an overflow condition, increment the minutes byte when needed and so on through to the year of the century byte. Also, each alarm byte is compared to its corresponding time byte, and an alarm is executed if there is a match or if a "DC" code (11XXXXXXX) is present in all three positions. A 32.768 KHz time base update takes 1,984 uS. During the update cycle, the time, calendar, and alarm bytes are inaccessible. The Update In Progress (UIP) status bit is set at this time.

There are three routines the processor may use to avoid the update cycle.

If the Update-Ended interrupt is enabled, an interrupt occurs every update cycle and over 999 mS are available to read valid data. Before leaving the interrupt service routine, the IRQF bit in Register C should be cleared.

The second routine uses the Update-In-Progress bit (UIP) in Register B to determine the status of the update. The UIP bit is set once per second. After the UIP bit goes High, the update begins 244 uS later. Therefore, the user has at least 244 uS, if the UIP bit is Low, to read valid data. Once the UIP bit is set, data is not valid and should not be used by the processor. Also, the user should avoid interrupt service routines that cause it to take longer than 244 uS to read time/calendar data.

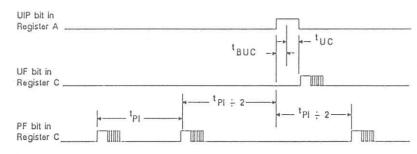

The third routine uses the periodic interrupt to determine if an update cycle is in progress. The UIP bit is set High between the setting of the PF bit in Register C. Periodic interrupts that occur at a rate greater than tBUC + tUC allow valid information to be read at each occurrence of the periodic interrupt. The reads should be done within (tPI + 2) + tBUC to insure valid data. See Figure 2-19 for more information on the update cycle.

PI = Periodic Interrupt Time Interval (500 ms, 250 ms, 125 ms, 62.5 ms, etc. per Figure 2 – 18) UC = Update Cycle Time (248 & or 1984 &) BUC = Delay Time Before Update Cycle (244 &s)

Figure 2-19 Update-ended and periodic Interrupt relationships

# **RTC** Registers

The RTC has four registers, A,B,C, and D, which are accessible by the 80286 processor during the update cycle. These registers are described below.

Register A -- A diagram of register A's bit functions is shown in Figure 2-20. These functions are described in the following paragraphs.

| ь7  | b6 | b5 | Ь4 | ь3  | b2  | ы   | ь0  |

|-----|----|----|----|-----|-----|-----|-----|

| UIP | x  | ×  | х  | RS3 | RS2 | RS1 | RS0 |

Figure 2-20 Register A bit functions

Update In Progress Bit (UIP) -- This is a status bit that can be monitored by the processor. If set to a "1", the update cycle is in progress or will be shortly. If a "0", an update will not occur for at least 244 uS. The time, calendar, and alarm data is all valid and accessible when the bit is "0". This bit is read only and ignores RESET; however, writing a "1" in the SET bit of Register B will prohibit updates and clear the UIP status bit.

Rate Selection Bits (RS3,RS2,RS1,RS0) -- These four bits select the rate the periodic interrupts will occur if the PIE bit in Register B is set to "1". These four bits are read/write, are not affected by RESET and are never changed by the RTC. See Figure 2-18.

Register B -- A diagram of register B's bit functions is shown in Figure 2-21. These functions are described in the following paragraphs.

| b7  | ь6  | b5  | b4  | b3 | b2 | b1    | ь0  |

|-----|-----|-----|-----|----|----|-------|-----|

| SET | PIE | AIE | UIE | х  | DM | 24/12 | DSE |

Figure 2-21 Register B bit functions

SET -- When the SET bit is a "0", the update cycle advances the count once per second. When SET is a "1", any update cycle in progress is aborted and the processor may initialize the time and calendar bytes without an update occurring. SET is a read/write bit and is not modified by RESET.

Periodic Interrupt Enable Bit (PIE) -- PIE is a read/write bit that allows the periodic interrupt flag (PF) bit to cause the IRQ pin to be driven High. The processor writes a "1" to the PIE bit in order to receive periodic interrupts at the rate selected by RS3, RS2, RS1, and RS0 in Register A. A "0" in PIE keeps IRQ inactive by a periodic interrupt, but the PF bit is still set at the periodic rate. PIE is cleared to "0" by RESET.

Alarm Interrupt Enable Bit (AIE) -- The AIE bit is a read/write bit which, when set to a "1", permits the alarm flag (AF) to assert IRQ. An alarm interrupt occurs for each second that the three time bytes equal their corresponding alarm bytes including the "DC" state. When AIE is "0", the AF bit does not set IRQ. The RESET pin clears AIE to "0".

Update-ended Interrupt Enable bit (UIE) -- The UIE bit is a read/write bit which enables the update-end flag (UF) bit to set IRQ. If the RESET pin or the SET bit is set to a "1", the UIE bit is cleared.

Data Mode Bit (DM) -- The DM bit indicates whether the time and data updates are to use binary or BCD formats. It is dependent only on the processor. A "1" indicates binary data, a "0" indicates BCD data.

24/12 Bit -- The 24/12 bit sets the format of the hours bytes as either the 24 hour mode, set to a "1" or the 12 hour mode, set to a "0". It is affected only by the processor.

Daylight Savings Enable Bit (DSE) -- The DSE bit is a read/write bit which allows the processor to enable two special updates when DSE is a "1". On the last Sunday in April, the time increments from 1:59:59 AM to 3:00:00 AM. On the last Sunday in October, the time changes from 1:59:59 AM to 1:00:00 AM. These times do not change when DSE is "0". DSE is not changed by any internal operations or RESET.

Register C -- A diagram of register C's bit functions is shown in Figure 2-22. These functions are described in the following paragraphs.

| b7   | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

|------|----|----|----|----|----|----|----|

| IROF | PF | AF | UF | 0  | 0  | 0  | 0  |

Figure 2-22 Register C bit functions

Interrupt Request Flag (IRQF) -- The IRQF flag is set to "1" if one or more of the following occur:

- PF = PIE = "1"

- AF = AIE = "1"

- UF = UIE = "1"

When IRQF is set to "1", the IRQ pin is driven Low. All flag bits are cleared after Register C is read or RESET is activated.

Periodic Interrupt Flag (PF) -- The PF flag is a read only bit. It is set to "1" when a particular edge is detected on the divider chain. This flag is cleared when Register C is read or by RESET.

Alarm Interrupt Flag (AF) -- When the AF bit is set to "1", the current time has matched the alarm time. A "1" causes IRQ to go High if AHE is also High ("1"). This also sets the IRQF bit. A RESET or Register C read clears AF.

Update-Ended Interrupt Flag (UF) -- This flag bit is set at the end of each update cycle. When UF and UIE are a "1", IRQF is set to "1" and IRQ goes High. UF is cleared by RESET or a Register C read.

B3 to B0 -- Unused bits of Register C, read as "0's". They cannot be written to.

Register D -- A diagram of register D's bit functions is shown in Figure 2-23. These functions are described in the following paragraphs.

| b7  | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

|-----|----|----|----|----|----|----|----|

| VRT | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

Figure 2-23 Register D bit functions

Valid RAM and Time Bit (VRT) -- The VRT bit indicates the condition of the contents of RAM provided the power sense (PS) pin of the chip is properly connected. A "0" appears when the PS pin is Low. The processor can set the VRT bit when the time and calendar are initialized. The VRT is a read only bit that cannot be modified by the RESET pin. The VRT bit can only be set by reading Register D.

b6 to b0 -- These unused bits are always read as "0's" and cannot be written to.

#### KEYBOARD INTERFACE

The processor board contains a port for a serial keyboard. The keyboard status and interface is provided by an Intel 8247 UPI controller chip, described below. The connector, J5, is a 10 pin dual jumper block. In addition to the signals used for keyboard control the connector also can input the POWER GOOD signal from the power supply on pin three. This signal is not required for keyboard operation.

The pin-out is listed in Figure 2-24. See Figure 1-1 or 1-2 for the location of this connector.

| SIGNAL     | PIN | DIRECTION      |

|------------|-----|----------------|

| + Clock    | 1   | Bl-directional |

| +Data      | 2   | Bi-directional |

| POWER GOOD | 3   | Input          |

| +5 Volts   | 4   | Output         |

| NC         | 5   |                |

| GROUND     | 6   |                |

| GROUND     | 7   |                |

| GROUND     | 8   |                |

| GROUND     | 9   |                |

| GROUND     | 10  |                |

Figure 2-24 Keyboard connector pin-out

# 8742 CONTROLLER

The two ports on the 8742 Universal Peripheral Interface (UPI) chip, U37, are used by the system for status and keyboard interface. They are described in Figure 2-25.

60H - GF

| DATA BIT | INPUT PORT               | OUTPUT PORT         |

|----------|--------------------------|---------------------|

| 0        | Unused C4H               | Reset system board  |

| 1        | Unused ( )               | Gate Address 20     |

| 2        | Unused                   | System speed switch |

| 3        | Unused                   | Unused              |

| 4        | Sense RAM size           | Output buffer full  |

|          | 0-Not supported          |                     |

|          | 1-512K on system board   |                     |

| 5        | Power-on default speed   | Input buffer empty  |

|          | 0-S2 pins 1-2 High speed |                     |

|          | 1-S2 pins 2-3 Low speed  |                     |

| 6        | Display type Switch S1   | Keyboard clock out  |

|          | 0-Color/Graphics         |                     |

|          | 1-Monochrome             |                     |

| 7        | Keyboard disable switch  | Keyboard data out   |

|          | 0-Keyboard disabled      |                     |

|          | 1-Keyboard enabled       |                     |

Figure 2-25 UPI port description

In addition to the input/output ports two test pins, 1 and 39, are used to sample keyboard data from the keyboard. Their functions are shown in Figure 2-26.

| T      | TEATA  | V - I d ala ali lanut |

|--------|--------|-----------------------|

| Pin 1  | TEST 0 | Keyboard clock input  |

| Pin 39 | TEST 1 | Keyboard data input   |

Figure 2-26 UPI test pin definitions

#### SOFTWARE SPEED SWITCHING

The board has provision for software speed switching. This option allows operation at two speeds. Proper jumper strapping is required for the selected speed; refer to the "Switches, Jumpers, and Adjustments" section of this manual. One speed is determined by the frequency of the primary crystal. This is fixed at 6.0 MHz. The second frequency is determined by the frequency of the crystal oscillator on the board. This oscillator must be between 6.0MHz and 10.0MHz. Figure 2-27 shows RAM speed/performance increase for different speed options.

| Wait<br>State | 6.0MHz    | 8.0MHz    | 10.0MHz       |

|---------------|-----------|-----------|---------------|

| 0             | 120ns/33% | 80ns/50%  | not available |

|               | 200ns/0%  | 150ns/25% | 120ns/40%     |

Figure 2-27 Speed/performance comparison

#### ADDRESS MAPS

Two types of addressing are defined for the 80286 CPU, memory and I/O. They are described below.

# Memory Address Map

The 24-bit address bus of the 80286 CPU defines a 16 MB physical address space. The 80286 operates in two addressing modes:

- The real address mode supports a 1MB address space. In this mode the 80286 is object code compatible with the 8088 and 8086 processors.

- The protected mode allows a 16 MB physical address space with a one gigabyte virtual address space. In protected mode some object code for the 8088 and the 8086 may require modification to support the virtual addressing requirements. The memory address map is shown in Figure 2-28.

| Memory Address    | Memory Type | Locations                                 |

|-------------------|-------------|-------------------------------------------|

| 000000H - 07FFFFH | 512 KB RAM  | SYSTEM BOARD                              |

| 080000H - 09FFFFH | 128 KB RAM  | SYSTEM BOARD OR<br>EXPANSION BOARD        |

| 0A0000H - 0BFFFFH | 128 KB RAM  | VIDEO DISPLAY                             |

| OCOOOOH - ODFFFFH | 128 KB ROM  | EXPANSION ROM FOR I/O BOARDS              |

| 0E0000H - EFFFFFH | 64 KB ROM   | SYSTEM BOARD ROM<br>DUPLICATED AT FE0000  |

| OFOOOOH - OFFFFFH | 64 KB ROM   | SYSTEM BOARD BIOS<br>DUPLICATED AT FF0000 |

| 100000H - FDFFFFH | 15 MB RAM   | EXPANSION RAM SPACE                       |

| FE0000H - FEFFFFH | 64 KB ROM   | SYSTEM BOARD ROM<br>DUPLICATED AT 0E0000  |

| FF0000H - FFFFFFH | 64 KB ROM   | SYSTEM BOARD BIOS<br>DUPLICATED AT 0F0000 |

Figure 2-28 Memory address map

# I/O Address Map

The 80286 CPU defines an I/O address map by dedicating ten address bits, A0-A9, to address 1KB of address space reserved for I/O instructions. The I/O address map includes I/O addresses reserved for specific devices in the expansion slots as well as dedicated system board I/O addresses.

Dedicated processor board I/O addresses are shown in Figure 2-29.

| ADDRESS     | DEVICE                                                                  |

|-------------|-------------------------------------------------------------------------|

| 000H - 01FH | DMA chip 1 (8237A-5)                                                    |

| 020H - 03FH | Interrupt controller 1 (8259A-2)                                        |

| 040H - 05FH | RTC VLSI                                                                |

| 060H - 06FH | Keyboard controller (8742)                                              |

| 070H - 07FH | RTC chip, DMA mask                                                      |